芯片(die)堆叠正在引起更多关注,但设计流程还没有完全准备好支持它。先进的封装技术被视为摩尔定律缩放的替代品,或者是一种增强它的方法。但是,为证明这些设备能够以足够的直通率来产量制造而给予的大量关注与对先进封装对设计和验证流程的要求之间存在巨大的差距。

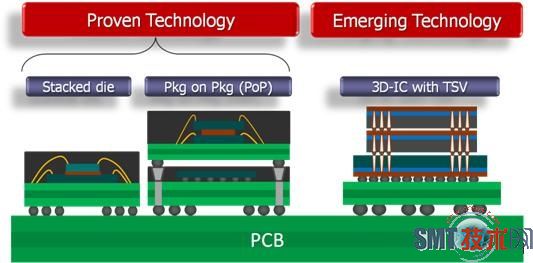

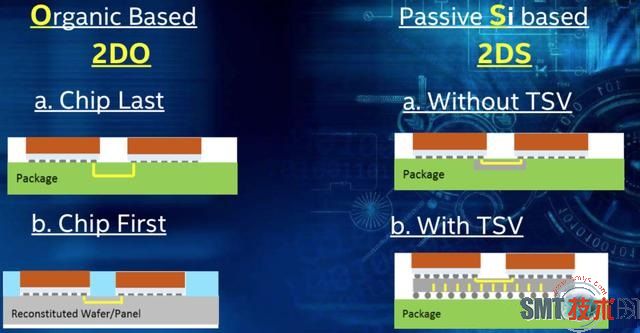

并非所有先进的封装都对工具和方法提出了相同的要求。 2.5D封装的要求与单片3D IC的要求大不相同。还有小芯片,各种类型的扇出和扇入,系统级封装方法,以及封装和直接键合方法。根据封装类型,可能需要混合使用PCB和IC设计技术和工具。无论使用哪种类型的封装,都可能需要添加各种形式的验证方法。

那么,行业在适应或增加必要的工具和流程以使更广泛的行业可以使用这项技术的地方在哪里?

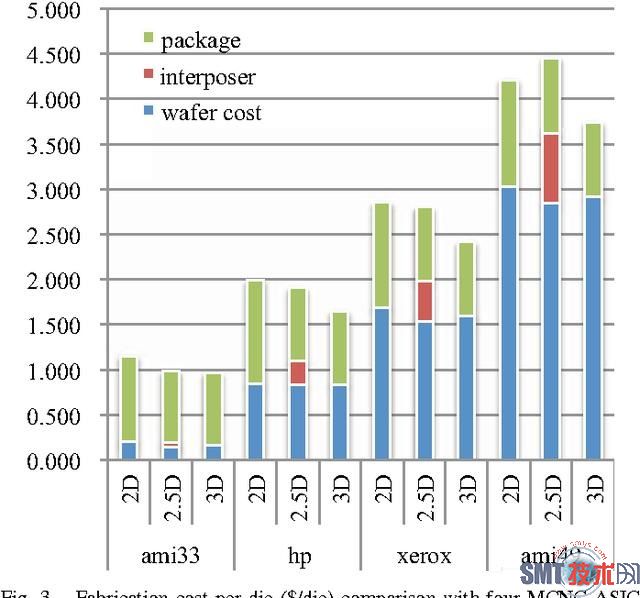

市场领导者始终是第一个转向最新节点的人,因为它为他们提供了维持竞争优势所需的扩展,功能和性能优势。 “对于大多数人来说,整体芯片单片扩展的形式即将结束,”西门子事业部Mentor董事会系统部产品营销经理Keith Felton说。 “7nm是非常昂贵的,每个晶圆的产量不是那么好,你必须制造数百万片芯片才能覆盖住NRE。当你的芯片规模很大时,你通常最好将设计分解成更小的块,你可以在芯片的那一部分使用适当的工艺节点或技术,然后将它们集成在一个硅插入器上。你会得到更便宜的东西。您可以更快地推向市场。如果你想进行更新,你可以只更换一个或两个小芯片并拥有一个新产品,而不必重新安装一个全新的SoC。“

虽然其中一些可能是对未来的预测,但它正是推动当今行业发展的动力。

“我们现在有一些目前成本相当高的选择,但它们有很多优势,”Cadence公司IC封装产品管理总监John Park说。 “在过去的几年里,我们一直在从小型PCB转变为开始看起来像一个大型集成电路。”

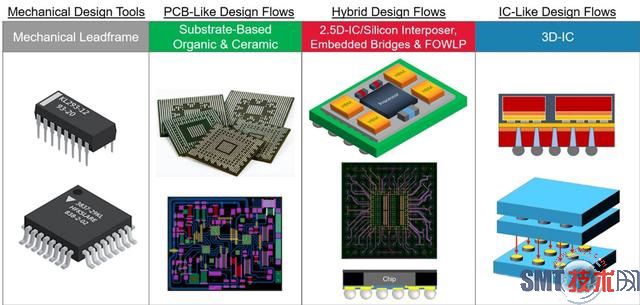

Park展示了该行业从引线框架到球栅阵列(BGA)以及现在的2.5D和3D技术(图1)所采用的工艺路径。

图1.封装技术和开发流程的演变。 资料来源:Cadence

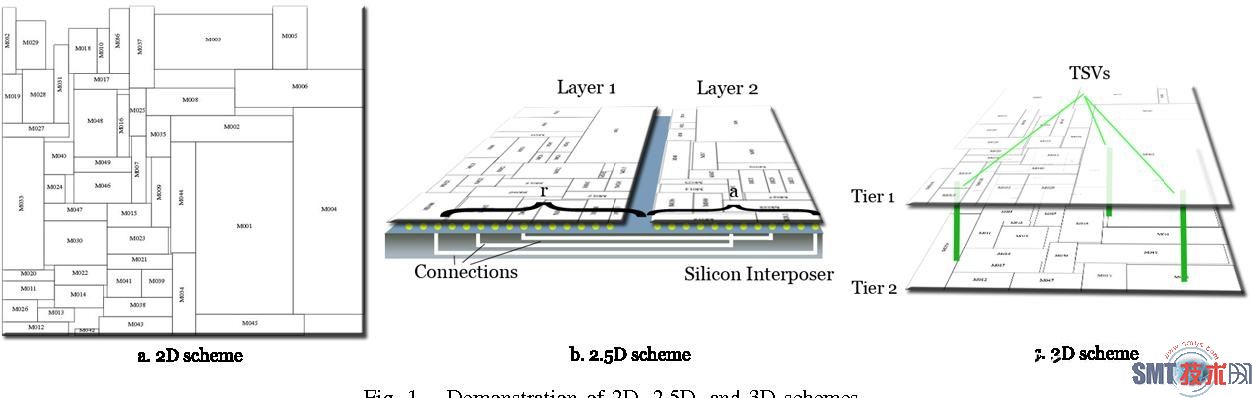

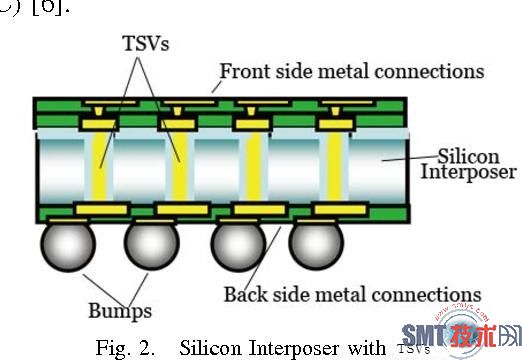

使用2.5D集成技术,您可以从电路板移动存储器并使用硅插入器将其集成到处理器旁边,这可以通过缩短距离和扩大数据管道来减少延迟。 “你用什么工具来实现插入器?”Park问道。 “你用什么走线(routing)和布局?怎么把它流片出去(tape out)?它需要以IC格式流片。从历史上看,封装采用PCB格式流程,例如Gerber或IPC2581格式的文件。“

这将对工具产生巨大影响。 “你需要一种类似PCB的技术来进行一些路由,因为它们在交互式和手动路由方面比传统的IC设计工具更加先进,而传统的IC工具往往是更多的批量应用,”他指出。 “但我还需要一些IC技术。我需要创建掩模层( mask layers)和GDS,因为它们将使用IC设计过程制造。一旦我们进入3D IC,这纯粹是一个IC过程。它从计划到签收,包括时序分析。另外,您需要多芯片(multiple-die)的LVS检查。封装设计师从电路板设计师变为芯片设计师。它还延伸到生态系统中,每个新的封装版本都需要参考工艺流程和相关的PDK。“

器件封装设计示例

器件封装设计

这不仅仅是一个工具变化。设计文化也随着工具而变化。 Mentor的技术营销工程师John Ferguson表示,“我很想知道在验证封装级别的装配设计方面存在多少刚性或者多少种格式。” “有一个粗略的设计规则手册,如果你遵循,你应该能够制造它。用户可以通过观察它来解决这个问题。但是没有人真正关心过。现在我们谈论的是数十万或数百万个引脚。能够通过观察它们进行检查的想法是不可能的。“

帮助这个行业的是一个名为CHIPS的DARPA项目计划,它推动了芯片概念的发展。 “在过去,所有的IP都在同一个工艺节点上,”Park解释道。 “现在你把它分开并以与节点无关的方式重建它。 SerDes可以是28nm,内存可以是32nm,7nm的视频芯片等等。我有那种灵活性。但它比这更复杂,因为小芯片是物理上实现的第三方IP版本”。“这些方面的流程需要在物理和协议级别上进行一些额外的工作。

整个封装是否需要作为单个芯片处理? “我们今天已经面临着对1亿门级的设计进行分析和验证的挑战,”Synopsys的3DIC布局和验证应用工程师Frank Malloy说。 “现在你在顶部堆叠另外1亿个门,如果你试图将它视为一个巨大的设计,你的内存使用和运行时将失去控制。我们需要抽象能够建模和封装设计的某些部分,并减少对内存和运行时的影响。“

器件封装设计

器件封装设计

但也有一些关键的信息,必须在各个部分之间共享。 “在当今复杂的设计中,IR跌落分析至关重要,”Malloy说。 “现在,当你在一个芯片die上面有另一个芯片die时,你必须计算一个大芯片die的IR压降,它必须从封装通过底部芯片die向顶部芯片die进行供电和接地。上芯片die的IR下降将受到下芯片die的IR下降的影响,因此我们必须进行多芯片die的IR下降分析。

在一个设计环境下将这些部件拉到一起是一种有吸引力的方式或降低复杂性。

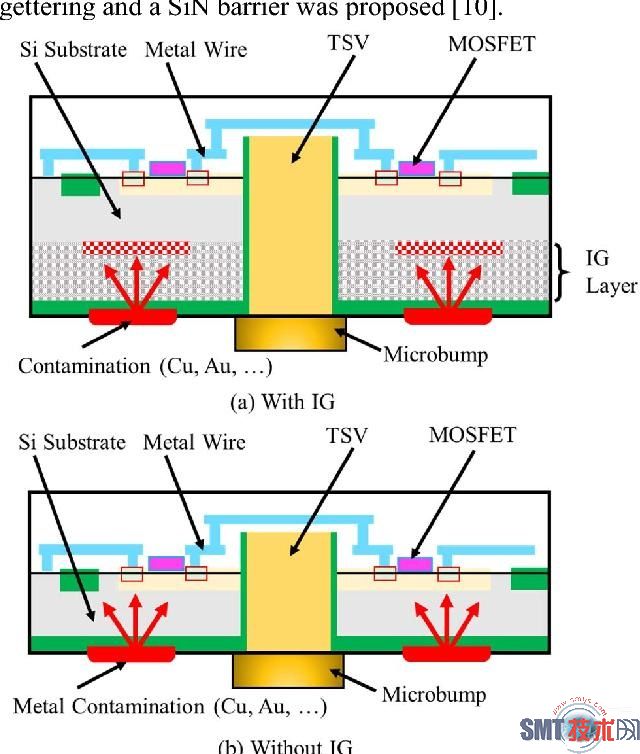

“基于模型的界面是任何试图将多个芯片die集成到系统中并尝试处理这些交互的人的优雅解决方案,”ANSYS模拟和混合信号解决方案高级产品经理Karthik Srinivasan说。 “IR下降可以以提取的方式完成,但是对于正在组装的系统并拥有真正的3D IC的人来说 - 一个芯片与凸点连接而另一个芯片通过微凸块馈送 - 在为了进行真正的IR分析时他们需要知道芯片die的负载。你需要一个并发模拟环境。“

芯片封装的设计成本

芯片封装设计

今天,那些抽象不是标准的。 “今天确实存在一些必要的抽象,但每个供应商都有自己的专业和自己的做事方式,”弗格森指出。 “在代工厂和用户之间,随着时间的推移,这将会合并,我们将全部采用相同的设计实践。”

最终,标准机构将参与进来。 “有些标准机构,例如Si2,正试图提出一些这些抽象的无IP定义,”费尔顿解释道。 “但是,今天存在很多格式。 它们可能不太理想,但它包括LEF / DEF文件,GDS文件,逗号分隔值电子表格,AIF文件到BGA.txt文件。 在早期,你必须要小心,你不要太严格。 这可能会迫使用户进入特定的使用模型。 我们已经看到客户在使用不同形式的数据攻击具有同一问题的非常多样化的数据格式。 他们想要的是一种尽可能开放的解决方案,因此他们不会被迫进入限制性数据流。“

在小芯片的概念成为现实之前,可能需要标准接口。 “高带宽内存(HBM)是一个早期的例子,”Park说。 “这有点容易,因为它只是一个针对特定应用程序的内存接口。小芯片接口必须更通用。“

DARPA CHIPS计划正在解决这个问题。他们选择了先进接口总线(AIB,Advanced Interface Bus)作为物理层接口,由英特尔开发,用于嵌入式多芯片互连桥(EMIB,Embedded Multi-Die Interconnect Bridge)中的芯片到芯片连接。英特尔通过DARPA计划提供AIB免版税。其他公司正在开发在此接口之上运行的轻量级协议。

但是可能需要多个专用接口。 “HBM是一个高度并行化的接口,您可以在不使用高速IO的情况下移动大量数据,”Felton解释道。 “它可以为您提供远远超出功耗的吞吐量,从而减少散热问题。有PAM4,那里有很多协议接口。根据芯片的类型及其功能,芯片组将根据所需的性能支持一个或多个标准接口。“

今天,必须设计封装,并且可能需要对设计进行分区。走线(Routing)可能涉及多个芯片。分析必须考虑到封装中的所有内容以及更多内容。

“几年前,一位包工程师花了90%的时间来实施,”Park说。 “这包括诸如布线设计,创建电源平面和进行电气特性描述等任务。如果你今天和同一个人谈话,那部分工作不到50%。他们花了很多时间在走线设计阶段与芯片团队合作。他们正试图根据成本,性能,物理特性和功耗来找出最适合该芯片的封装技术。“

这在多个层面上变得复杂。 “你可能有六个小芯片,你可能有不同类型的内存,无论是堆叠还是并排,你可能正在考虑使用插入器或嵌入式插入器桥,”Felton补充道。 “您基本上处理多层次的基板集成,并排,堆叠,嵌入,您需要一个可以快速评估这些不同场景的环境,以便了解它们在总体目标方面为您提供的服务。”

芯片封装的设计应用

芯片封装的设计应用

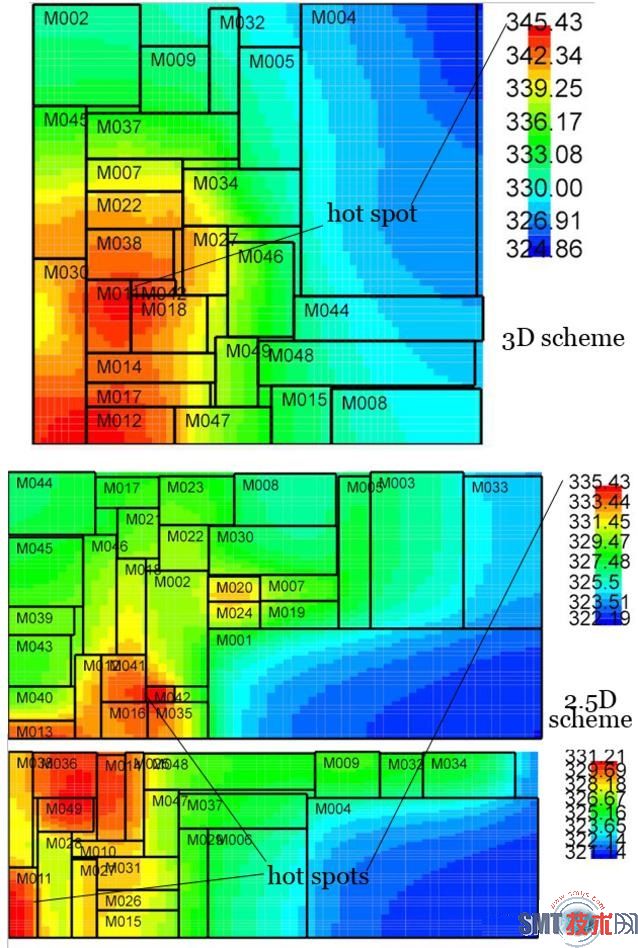

但设计流程是可以看到主要影响的地方。 “我们已经修改了芯片设计链中的每一个工具,从实施到验证,包括物理设计,静态时序分析,寄生参数提取,设计规则检查(DRC)和LVS,”Malloy说。 “这些工具中的每一个都得到了增强,以支持3D设计。大多数设计今天都是单独完成的,但是在流程中的某些时候你将它们组合在一起。然后我们需要读取两个裸片并查看它们之间的优化。我们应该在哪里移动凸块,以便通过两个芯片die获得最短的导线长度?我们应该在哪里移动bumps(电源)或门电路(逻辑gates),以便我们通过它们两者获得最快的时间?我们最近对提取和分析进行了改进,以便能够查看两个裸片并查看两个裸片之间的导线上可能发生的电容耦合。现在这些具有混合键合的裸片非常接近,因此两者的最顶层金属层可以相互作用,并且在两种完全不同的设计之间具有电容耦合。

还有更多的事情要来。 “你不再只有两个维度,现在你有第三个维度,”帕克说。 “从理论上讲,你有20多个金属层可以玩,因为你有两个面对面的芯片die。如果我在同一芯片上将两个功能块彼此相邻放置,但由于其他限制,它们距离太远,我可以移动一个功能块到它上面的芯片中。这有什么用?它是如何工作的?它有何种影响?路由(Routing)成为一个三维问题。如果底部芯片上的路由资源耗尽,即使您尝试连接底部芯片上的两个旗舰,您也有可能通过过孔(via)的方式到顶部芯片并在该芯片上找到路由资源然后过孔回到底部。你必须在两个三维堆叠的芯片上进行时序收敛。“

先进的器件封装设计

先进的器件封装设计

高级封装的重新工具化才刚刚开始。虽然EDA公司不能停止投资遵循最新实施的工艺节点,但他们还必须大力投资新的封装技术的设计流程。与仅影响后端工具的最新工艺节点的更新不同,封装设计将影响设计流程中的所有内容,并为全新工具添加一些要求。

他们需要多长时间才能实现这些目标? “在过去,公司正在收集数据,但在短期内并没有真正计划任何事情,”弗格森说。 “今天,虽然它仍在进行实验,但它不再只是踢轮胎了。 他们决定买一辆车,他们正试图确定将哪辆车带回家。“